2014-09-22

# Altera JESD204B IP Core and TI DAC37J84 Hardware Checkout Report

AN-719 Subscribe Send Feedback

The Altera JESD204B MegaCore function is a high-speed point-to-point serial interface intellectual property (IP).

The JESD204B IP core has been hardware-tested with a number of selected JESD204B-compliant ADC (analog-to-digital converter) and DAC (digital-to-analog) devices.

This report highlights the interoperability of the JESD204B IP core with the DAC37J84 converter evaluation module (EVM) from Texas Instruments Inc. (TI). The following sections describe the hardware checkout methodology and test results.

# **Hardware Requirements**

The hardware checkout test requires the following hardware and software tools:

- Altera Stratix V Advanced Systems Development Kit with 15 V power adaptor

- HSMC breakout board included in the Stratix V Advanced Systems Development Kit

- TI DAC37J84 EVM with 5.0 V power adaptor

- Mini-USB cables

- SMA cables

- Wire for connecting J21 header to HSMC breakout board header

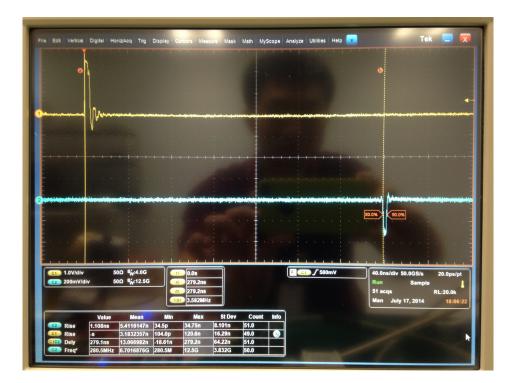

- Oscilloscope with a minimum bandwidth of 4 GHz

# **Hardware Setup**

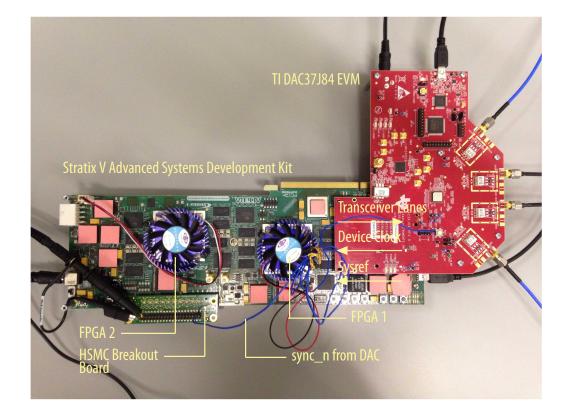

A Stratix V Advanced Systems Development Kit is used with the TI DAC37J84 daughter card module installed to the development board's FMC connector.

- The DAC37J84 EVM derives power from 5.0 V power adaptor.

- The FPGA and DAC device clock is supplied by the LMK04828 clock generator on the DAC37J84 EVM.

- For subclass 1, the LMK04828 clock generator generates *SYSREF* for the JESD204B IP core as well as the DAC37J84 device.

- The sync\_n signal is transmitted from the DAC37J84 to FPGA through a wire connected to J21 (pin 1) of DAC37J84 EVM and HSMC breakout board (pin 3). <sup>(1)</sup>

ISO 9001:2008 Registered

low part of Inte

\*Other names and brands may be claimed as the property of others.

#### Figure 1: Hardware Setup

<sup>&</sup>lt;sup>(1)</sup> The sync\_n signal from the DAC does not have direct connection to FPGA 1 through the FMC connector. The FPGA 2 is used as a bridge to transfer the sync\_n signal to FPGA 1 through the HSMC connector.

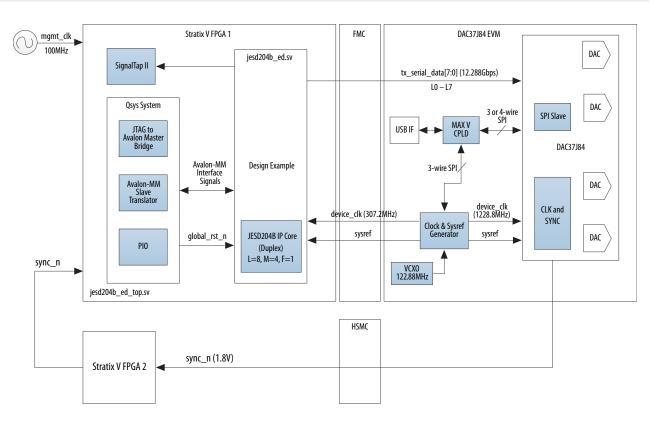

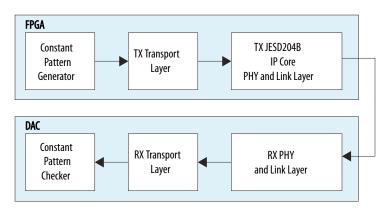

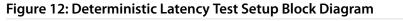

The system-level diagram shows how the different modules connect in this design.

In this setup, where LMF = 841, the data rate of transceiver lanes is 12.288 Gbps. The LMK04828 clock generator provides 307.2 MHz device clock to the FPGA and 1228.8 MHz device clock to the DAC37J84 device. The LMK04828 provides *SYSREF* pulses to both the DAC and FPGA. A wire connects between J21 pin 1 on DAC37J84 EVM (SYNC\_N\_AB pin) and HSMC breakout board header pin 3 to transmit the sync\_n signal from DAC37J84 to FPGA 2. The FPGA 2 acts as a passthrough to deliver sync\_n signal to FPGA 1. The DAC37J84 operates in LINK0 only mode (single link) in all configurations.

Note: The FPGA 2 must be configured prior to connecting the wire that carries the sync\_n signal to the HSMC breakout board header. Verify that the voltage at the targeted header pin is less than 1.8 V. Refer to the DAC37J84 datasheet for the absolute maximum rating of SYNC\_N\_AB pin.

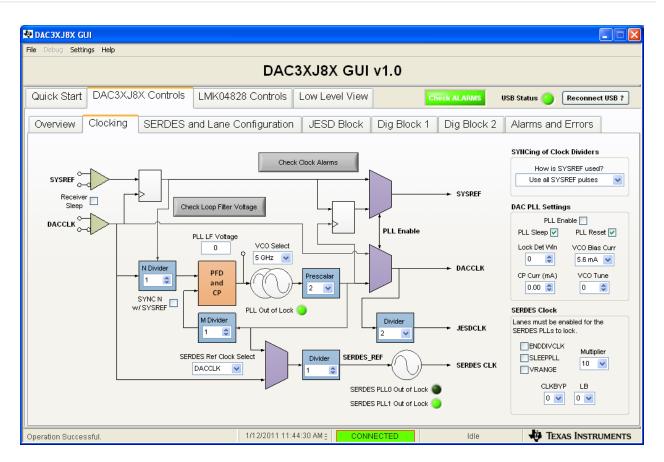

## DAC3XJ8XEVM Software Setup

The DAC3XJ8XEVM software configures the DAC37J84 device and LMK04828 clock generator for JESD204B link operation.

You need to configure the DAC and LMK04828 with the correct settings and sequence for the JESD204B link to operate at the targeted data rate and JESD204B link parameters. Follow these steps to set up the configuration via the DAC3XJ8XEVM graphical user interface (GUI):

Send Feedback

3

#### DAC3XJ8XEVM Software Setup

4

- 1. Configure the FPGA.

- In the Quick Start tab, select a value for DAC Data Input Rate, Number of SerDes Lanes, and Interpolation options to meet the settings as stated in Table 6. The DAC device clock is synonymous to the DAC Output Rate.

- 3. Click the 1. Program LMK04828 and DAC3XJ8X button.

- 4. In the DAC3XJ8X Controls tab, select the Clocking sub tab. For the SYNCing of Clock Dividers drop-down list, select Use all SYSREF pulses.

- 5. In the DAC3XJ8X Controls tab, select the JESD Block sub tab.

- a. At the *Elastic Buffer* section, turn on the Match Char. checkbox.

- b. At the Initialization Bits section, turn off the TX Does not allow lane syncing checkbox.

- **c.** Change the K and RBD value accordingly. RBD value is K value minus 1. For example, when K = 32, set RBD = 31.

- **d.** At the *Configuration for All Lanes* section, for the **SCR** drop-down list, select **SCRAMBLE ON** if scrambler is turned on at the JESD204B IP core. Select **SCRAMBLE OFF** if scrambler is turned off at the JESD204B IP core.

- e. At the *Errors for SYNC Request and Reporting* section, under the Link0 S column, turn on the Link configuration error, 8b/10b not-in-table code error, and 8b/10b disparity error checkboxes. Optionally, you can turn off all the checkboxes under the Link1 S R columns.

- 6. In the LMK04828 Controls tab, select the SYSREF and SYNC sub tab.

- a. At the FPGA Clock and SYSREF section, turn on the HS checkbox for DCLK Delay.

- **b.** At the *SYSREF Configuration* section, change the **SYSREF Divider** value according to the mode and K value of the targeted operation:

- a. LMFS=148, K=16 and 32, SYSREF Divider=768

- **b.** LMFS=244, K=16 and 32, SYSREF Divider=512

- c. LMFS=4421, K=16 and 32, SYSREF Divider=256

- d. LMFS=8411, K=20, SYSREF Divider=80

- e. LMFS=8411, K=32, SYSREF Divider=128

- c. For the SYSREF Source drop-down list, select Normal SYNC.

- **d.** At the *SYNC Configuration* section, set the following:

- a. For the SYNC Mode drop-down list, select Pin.

- **b.** Turn off the **SYSREF SYNC Disable**, **DCLKout0 SYNC Disable**, and **DCLKout2 SYNC Disable** checkboxes.

- c. Turn on the SYNC Pin Polarity checkbox. Then turn off this option.

- **d.** Turn on the **SYSREF SYNC Disable**, **DCLKout0 SYNC Disable**, and **DCLKout2 SYNC Disable** checkboxes.

- e. At the *SYSREF Configuration* section, for the **SYSREF Source** drop-down list, select **SYSREF Pulses**.

- In the Quick Start tab, click the 2. Reset DAC JESD Core button. Then, click the 3. Trigger LMK04828 SYSREF button

You can record steps 4 to 6 in a log file for future replay. Double-click the lower left corner (see Figure 3) of the software. A pop-up Status Log window is launched. Right click at the empty area and select "Clear Log" and close the pop-up window. Perform steps 4 to 6. Re-open the pop-up window and select the series of actions that are recorded. Right click at the empty area and save the selected actions into a file with .cfg extension. Use an editor to delete the read register records. Then transform the write register records into

the format as indicated in the sample setup files that are included in the graphical user interface (GUI) installation. A sample configuration file for the LMF=841, K=32, RBD=31, SCR=1 is shown below.

```

DAC3XJ8X

0x51 0x00FF //enable sync request for link 0

0x54 0x0000 //disable sync request for link 1

0x55 0x0000 //disable error reporting for link 1

0x4F 0x1CC1 //turn on lane sync, match specific character 0x1C to start JESD

buffering

0x4C 0x1F07 //K=32, L=8

0x4B 0x1E00 //RBD=31, F=1

0x4E 0x0F6F //SCR=1, HD=1

0x24 0x0010 //cdrvser_sysref_mode=use all sysref pulses

LMK04828

0x13A 0x00 //sysref divider=128

0x13B 0x80 //sysref divider=128

0x104 0x60 //half step for FPGA device clk

0x139 0x00 //set SYSREF_Mux to "Normal"

0x143 0x11 // trigger SYNC event using "Pin" mode

0x144 0x00 //enable syncing of all clock outputs

0x143 0x31 //toggle SYNC Pin Polarity bit

0x143 0x11 //toggle SYNC Pin Polarity bit

0x144 0xFF //disable syncing of all clock outputs

0x139 0x02 //set SYSREF_MUX to "Pulses"

```

The figures below show the examples of GUI setup for LMF = 841 configuration.

#### Figure 3: Quick Start Tab

| DAC3XJ8X GUI        |                                            | 1                            | 1                     | The second                     |                              |  |  |  |

|---------------------|--------------------------------------------|------------------------------|-----------------------|--------------------------------|------------------------------|--|--|--|

| File Debug Set      | File Debug Settings Help DAC3XJ8X GUI v1.0 |                              |                       |                                |                              |  |  |  |

| Quick Start         |                                            |                              |                       |                                |                              |  |  |  |

| Quick Otart         | DACSASOA CONTIONS                          | LINK04020 CONTOIS            | LOW Level View        | Check ALARMS                   | USB Status 🥘 Reconnect USB ? |  |  |  |

|                     |                                            |                              |                       |                                |                              |  |  |  |

|                     |                                            |                              |                       |                                |                              |  |  |  |

| Ste                 | p 1 - Choose Clock Mode Ste                | p 2 - Choose DAC Configurati | on                    | Step 3 - Stats!                |                              |  |  |  |

|                     | EVM Clocking Mode                          |                              | umber of SerDes Lanes | DAC Output Rate<br>1228.8 MSPS | JESD204B Mode (LMFS)<br>8411 |  |  |  |

|                     | Onhoard                                    |                              | erpolation            | FPGA Clock                     | SerDes Linerate              |  |  |  |

|                     |                                            | 1228.8 <b>wsps</b> 1         |                       | 307.2 MHz                      | 12288 Mbps                   |  |  |  |

|                     |                                            |                              |                       |                                |                              |  |  |  |

|                     | Step 4 - Program EV                        | /M                           |                       |                                |                              |  |  |  |

|                     | Programming Ord<br>1. Program LMK04        | 1020 1. Program LMP          |                       |                                | 4828                         |  |  |  |

|                     | toggle DAC RES<br>program DAC3             | ETB Pin, and DAC3X<br>KJ8X   |                       | SYSREF                         |                              |  |  |  |

|                     | 2. Reset DAC JES<br>3. Trigger SYSREF      |                              |                       |                                |                              |  |  |  |

|                     |                                            |                              |                       |                                |                              |  |  |  |

| Quick Start Message |                                            |                              |                       |                                |                              |  |  |  |

|                     |                                            |                              |                       |                                |                              |  |  |  |

|                     |                                            |                              |                       |                                |                              |  |  |  |

|                     |                                            |                              |                       |                                |                              |  |  |  |

| Read Register: DA   | C3XJ8X.config108[0x6C] - [0x7              | ] 1/12/2011 11:              | 44:30 AM CONNE        | CTED Idle                      | TEXAS INSTRUMENTS            |  |  |  |

Altera JESD204B IP Core and TI DAC37J84 Hardware Checkout Report

**Altera Corporation**

#### Figure 4: DAC3XJ8X Controls Tab - Clocking

### Figure 5: DAC3XJ8X Controls Tab - SERDES and Lane Configuration

| 😻 DAC3XJ8X GUI                                                                                                                                         | the state of the second state                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                     |                                                         |                   |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|-------------------|--|--|--|

| File Debug Settings Help                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                     |                                                         |                   |  |  |  |

| DAC3XJ8X GUI v1.0                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                     |                                                         |                   |  |  |  |

| Quick Start         DAC3XJ8X Controls         LMK04828 Controls         Low Level View         Check ALARMS         USB Status         Reconnect USB ? |                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                     |                                                         |                   |  |  |  |

| Overview Clocking SE                                                                                                                                   | RDES and Lane Configuration                                                                                                                                                                                                                                                                                                                                                                       | JESD Block D                                                                                                                                                                        | Dig Block 1 Dig Block 2                                 | Alarms and Errors |  |  |  |

| SERDES Configuration                                                                                                                                   | EN       Invert?       Lane ID       Which RX         RX0       V       3       3       3         RX1       V       2       2       2         RX2       V       1       1       1         RX3       V       0       0       0       0         RX4       V       7       5       9       7         RX6       V       6       6       6       9         RX7       V       5       4       4       9 | and 20-bit<br>, LOS and<br>dos on the linerate.<br>y SERDES lane can<br>lap to Lane" field,<br>d match the lane ID<br>o<br>o<br>o<br>o<br>o<br>o<br>o<br>o<br>o<br>o<br>o<br>o<br>o | Equalizer,<br>Sampler,<br>Descrializer,<br>and<br>FIFOS | JESD Block        |  |  |  |

| Operation Successful.                                                                                                                                  | 1/12/2011 11:4                                                                                                                                                                                                                                                                                                                                                                                    | 14:30 AM CONNEC                                                                                                                                                                     | TED Idle                                                | TEXAS INSTRUMENTS |  |  |  |

Send Feedback

l

7

### Figure 6: DAC3XJ8X Controls Tab - JESD Block

| DAC3XJ8X GUI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                            |                                      |                                                       |                                                                                                                                                                                                                 |                                                                                                                                                                                                                                 |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|-------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| File Debug Settings Help                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | File Debug Settings Help                                                                                                                   |                                      |                                                       |                                                                                                                                                                                                                 |                                                                                                                                                                                                                                 |  |

| DAC3XJ8X GUI v1.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                            |                                      |                                                       |                                                                                                                                                                                                                 |                                                                                                                                                                                                                                 |  |

| Quick Start DAC3XJ8X Controls                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | LMK04828 Contro                                                                                                                            | Is Low Leve                          | el View                                               | Check ALARMS                                                                                                                                                                                                    | USB Status 🧿 Reconnect USB ?                                                                                                                                                                                                    |  |

| Overview Clocking SERDES a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | nd Lane Configurat                                                                                                                         | ion JESD E                           | Block Dig E                                           | Block 1 Dig Block 2                                                                                                                                                                                             | Alarms and Errors                                                                                                                                                                                                               |  |

| JESD Configuration:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                            | Elastic Buffer                       |                                                       |                                                                                                                                                                                                                 | Configuration for All Lanes                                                                                                                                                                                                     |  |

| First, set the "Configuration for All Lanes" and then<br>configurations. These values should match the con-<br>link configuration, including Lane ID on the SERDES<br>configuration error" will occur. Next, configure the S<br>errors that will trigger a SYNC request. Generally, a<br>SYNC request. The currently encountered errors c<br>"Alarms and Errors" page. After everything is confi-<br>below.<br>Initialization Bits<br>DESD RESET<br>OFF ♥ OFF ♥ Comma Align EN<br>OFF ♥ Comma Align EN<br>TX Does not allow<br>lane syncing | figuration in the transmitter<br>tab, otherwise a "Link<br>SYNC lines and choose the<br>Ill errors should trigger a<br>an be viewed on the | less than or (<br>equal to K.<br>RBD | Char. to Match bu<br>x 1C aft<br>se<br>Match what? ch | sable "Match Char." if<br>ffering should start right<br>ter the last M/C character is<br>int. Otherwise, a specific<br>ar is used to trigger the start<br>x1C = /R/ char).<br>Tans<br>port<br>upper of DC Block | L M F K S<br>8 4 1 32 1<br>N JESDV<br>16 16 JESD204B V<br>SUBCLASSV RES1 RES2<br>Subclass 1 0 0 0<br>SCR HD<br>SCRAMBLE ON ON V<br>Link0 Configuration<br>DD BID ADJCNT PHADJ<br>0 0 0 0<br>ADJDIR CS CF Lane Skew<br>0 0 0 0 0 |  |

| Errors for SYIIC Request and Reporting<br>Link0 Link1 S = Enable SYNC Request<br>S R S R R = Enable Error Reporting                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                            | 3n ment                              |                                                       |                                                                                                                                                                                                                 | How is SYSREF used?<br>Skip one pulse then use next V<br>Link1 Configuration                                                                                                                                                    |  |

| Multi-frame alignment error     Frame alignment error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                            |                                      |                                                       |                                                                                                                                                                                                                 | DID BID ADJCNT PHADJ                                                                                                                                                                                                            |  |

| V       Frame alignment error         Unk configuration error       Link configuration error         V       Elastic buffer overflow         V       Sb/10b nct-in-table code error         V       Bb/10b disparity error                                                                  | SYNCB (LVDS)<br>SYNCB Sleep -<br>SYNC_N_AB (CMOS)<br>Invert CMOS -<br>SYNC_N_CD (CMOS)                                                     |                                      | e mob form                                            | AN<br>SYNCB Link0 V<br>YNC_AB Link0 V<br>YNC_CD Link1 V                                                                                                                                                         | 0 0 0 0 0<br>ADJDIR CS CF<br>0 0 0<br>How is SYSREF used?<br>Skip one pulse then use next                                                                                                                                       |  |

| Read Register: DAC3XJ8X.config75[0x4B] - [0x1E0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 00] 1/12/2011                                                                                                                              | 11:44:30 AM E                        | CONNECTED                                             | Idle                                                                                                                                                                                                            | 🐺 Texas Instruments                                                                                                                                                                                                             |  |

### Figure 7: LMK04828 Controls Tab - SYSREF and SYNC

| DAC3XJ8X GUI v1.0                                                   |                                      |                               |                                                                                                |                                      |                                          |                                                                                |

|---------------------------------------------------------------------|--------------------------------------|-------------------------------|------------------------------------------------------------------------------------------------|--------------------------------------|------------------------------------------|--------------------------------------------------------------------------------|

| uick Start DAC3                                                     | XJ8X Controls                        | MK04828 Controls              | Low Level View                                                                                 | Check AL                             | ARMS USB Status                          | Reconnect USB ?                                                                |

| PLL1 Configuration                                                  | PLL2 Configura                       | ation SYSREF an               | d SYNC Clock                                                                                   | Outputs                              |                                          |                                                                                |

| SYSREF Configuration                                                |                                      | Global DDLY SY                | YNC Configuration                                                                              |                                      |                                          |                                                                                |

| SYSREF Source                                                       | SYSREF Divider                       | DDLY Step Count               | SYNC Mode                                                                                      |                                      | EF must be configured<br>ring will work. |                                                                                |

| SYSREF Block PD SYSREF PD SYSREF DDLY PD SYSREF PD SYSREF PUIser PD | Pulse Count                          | SYSREF DDLY<br>8              | SYSREF SYNC Disable<br>DCLKout0 SYNC Disable<br>DCLKout2 SYNC Disable<br>DCLKout4 SYNC Disable | DCLKout8 SYNC I     DCLKout10 SYNC I | Disable 🔽<br>Disable 🔽                   | SYNC Pin Polarity<br>SYNC Enable<br>SYNC until PLL2 DLD<br>SYNC until PLL1 DLD |

| CLKout Delays                                                       |                                      |                               |                                                                                                |                                      |                                          |                                                                                |

| CLKout 0 and 1<br>FPGA Clock & SYSREF                               | CLKout 2 and 3<br>DAC Clock & SYSREF | CLKout 4 and 5<br>Not Used    | CLKout 6 and 7<br>SMP Clock Outputs                                                            | CLKout 8 and 9<br>Extra FMC Clocks   | CLKout 10 and 11<br>Not Used             | CLKout 12 and 13<br>Extra FMC Clocks                                           |

| DCLK Delay<br>Dynamic DDLY EN                                       | DCLK Delay<br>Dynamic DDLY EN        | DCLK Delay<br>Dynamic DDLY EN | DCLK Delay<br>Dynamic DDLY EN                                                                  | DCLK Delay<br>Dynamic DDLY EN        | DCLK Delay<br>Dynamic DDLY EN            | DCLK Delay<br>Dynamic DDLY EN<br>DCLK Continuous?                              |

| HS #High #Low<br>▼ 5 ▼ 5 ▼                                          | HS #High #Low                        | HS #High #Low                 | HS #High #Low<br>5 • 5 •                                                                       | HS #High #Low                        | HS #High #Low                            | HS #High #Low                                                                  |

| ADLY Input Divider Only                                             | ADLY Input<br>Divider Only           | ADLY Input<br>Divider Only    | ADLY Input<br>Divider Only                                                                     | ADLY Input<br>Divider Only           | ADLY Input<br>Divider Only               | ADLY Input<br>Divider Only                                                     |

| ADLY (ps) 500                                                       | ADLY (ps) 500                        | ADLY (ps) 500                 | ADLY (ps) 500                                                                                  | ADLY (ps) 500                        | ADLY (ps) 500                            | ADLY (ps) 500                                                                  |

| SDCLK Delay                                                         | SDCLK Delay                          | SDCLK Delay                   | SDCLK Delay                                                                                    | SDCLK Delay                          | SDCLK Delay                              | SDCLK Delay                                                                    |

| HS ADLY EN DDLY ADLY (ps)                                           | HS ADLY EN DDLY ADLY (ps)            | HS ADLY EN DDLY ADLY (ps)     | HS ADLY EN DDLY ADLY (ps)                                                                      | HS ADLY EN                           | HS ADLY EN DDLY ADLY (ps)                | HS ADLY EN DDLY ADLY (ps)                                                      |

|                                                                     |                                      |                               |                                                                                                |                                      |                                          |                                                                                |

Altera JESD204B IP Core and TI DAC37J84 Hardware Checkout Report

#### Figure 8: LMK04828 Controls Tab - Clock Outputs

| Debug Settings He                     | p                                                          |                                                            |                                                                  |                                                                  |                                                                  |                                                                  |

|---------------------------------------|------------------------------------------------------------|------------------------------------------------------------|------------------------------------------------------------------|------------------------------------------------------------------|------------------------------------------------------------------|------------------------------------------------------------------|

|                                       |                                                            | DAC                                                        | 3XJ8X GUI                                                        | v1.0                                                             |                                                                  |                                                                  |

| uick Start DAC3                       | XJ8X Controls LM                                           | /K04828 Controls                                           | Low Level View                                                   | Check AL                                                         | ARMS USB Status                                                  | Reconnect USB ?                                                  |

| PLL1 Configuration                    | PLL2 Configura                                             | ation SYSREF ar                                            | nd SYNC Clock (                                                  | Outputs                                                          |                                                                  |                                                                  |

| CLKout 0 and 1<br>FPGA Clock & SYSREF | CLKout 2 and 3<br>DAC Clock & SYSREF                       | CLKout 4 and 5<br>Not Used                                 | CLKout 6 and 7<br>SMP Clock Outputs                              | CLKout 8 and 9<br>Extra FMC Clocks                               | CLKout 10 and 11<br>Not Used                                     | CLKout 12 and 13<br>Extra FMC Clocks                             |

| Group Powerdown                       | Group Powerdown<br>Output Drive Level<br>Input Drive Level | Group Powerdown<br>Output Drive Level<br>Input Drive Level | Group Powerdown 📝<br>Output Drive Level 📄<br>Input Drive Level 🗐 | Group Powerdown 🕼<br>Output Drive Level 🗍<br>Input Drive Level 📄 | Group Powerdown 📝<br>Output Drive Level 🗍<br>Input Drive Level 🥅 | Group Powerdown 📝<br>Output Drive Level 🥅<br>Input Drive Level 🥅 |

| DCLK Divider                          | DCLK Divider                                               | DCLK Divider                                               | DCLK Divider                                                     | DCLK Divider                                                     | DCLK Divider                                                     | DCLK Divider                                                     |

| 8 🗸                                   | 2 🗸                                                        | 8 💌                                                        | 24 💌                                                             | 16 💌                                                             | 8 💌                                                              | 8 💌                                                              |

| DCLK Source                           | DCLK Source                                                | DCLK Source                                                | DCLK Source                                                      | DCLK Source                                                      | DCLK Source                                                      | DCLK Source                                                      |

| Divider + DCC + HS                    | Divider + DCC + HS 👻                                       | Divider 👻                                                  | Divider 👻                                                        | Divider                                                          | Divider 🗨                                                        | Divider                                                          |

| DCLK Type Invert                      | DCLK Type Invert                                           | DCLK Type Invert                                           | DCLK Type Invert                                                 | DCLK Type Invert                                                 | DCLK Type Invert                                                 | DCLK Type Invert                                                 |

| LVDS V                                | LVPECL 2000 mV                                             | Powerdown 💌                                                | Powerdown 💌                                                      | LVDS V                                                           | Powerdown 💌                                                      | LVDS -                                                           |

| SDCLK Source                          | SDCLK Source                                               | SDCLK Source                                               | SDCLK Source                                                     | SDCLK Source                                                     | SDCLK Source                                                     | SDCLK Source                                                     |

| SYSREF -                              | SYSREF -                                                   | Device Clock                                               | SYSREF -                                                         | Device Clock                                                     | Device Clock                                                     | SYSREF -                                                         |

| SDCLK Type Invert                     | SDCLK Type Invert                                          | SDCLK Type Invert                                          | SDCLK Type Invert                                                | SDCLK Type Invert                                                | SDCLK Type Invert                                                | SDCLK Type Invert                                                |

| LVDS V                                | LCPECL -                                                   | Powerdown 💌                                                | Powerdown 💌                                                      | LVDS -                                                           | Powerdown 💌                                                      | Powerdown 💌                                                      |

| SDCLK EN/DIS State                    | SDCLK EN/DIS State                                         | SDCLK EN/DIS State                                         | SDCLK EN/DIS State                                               | SDCLK EN/DIS State                                               | SDCLK EN/DIS State                                               | SDCLK EN/DIS State                                               |

| Active/Active                         | Active/Active                                              | Active/Active                                              | Active/Active                                                    | Active/Active                                                    | Active/Active                                                    | Active/Active                                                    |

| SDCLKout_PD                           | SDCLKout_PD                                                | SDCLKout_PD                                                | SDCLKout_PD                                                      | SDCLKout_PD                                                      | SDCLKout_PD                                                      | SDCLKout_PD                                                      |

| DCLKout_DDLY_PD                       | DCLKout_DDLY_PD                                            | DCLKout DDLY PD                                            | DCLKout DDLY PD                                                  | DCLKout DDLY PD                                                  | DCLKout DDLY PD                                                  | DCLKout_DDLY_PD                                                  |

| DCLKout_HSg_PD                        | DCLKout_HSg_PD                                             | DCLKout HSg PD                                             | DCLKout_HSg_PD                                                   | DCLKout HSg PD                                                   | DCLKout_HSg_PD                                                   | DCLKout_HSg_PD                                                   |

| DCLKout ADLYg PD                      | DCLKout ADLYg PD                                           | DCLKout ADLYg PD                                           | DCLKout ADLYg PD                                                 | DCLKout ADLYg PD                                                 | DCLKout ADLYg PD                                                 | DCLKout ADLYg PD                                                 |

| DCLKout ADLY PD                       | DCLKout ADLY PD                                            | DCLKout ADLY PD                                            | DCLKout ADLY PD                                                  | DCLKout_ADLY_PD                                                  | DCLKout_ADLY_PD                                                  | DCLKout_ADLY_PD                                                  |

The LMK04828 clocks:

- CLKout0 supplies device clock to the FPGA.

- CLKout1 is configured as the SYSREF source for the FPGA.

- CLKout2 supplies device clock to the DAC.

- CLKout3 is configured as the SYSREF source for the DAC.

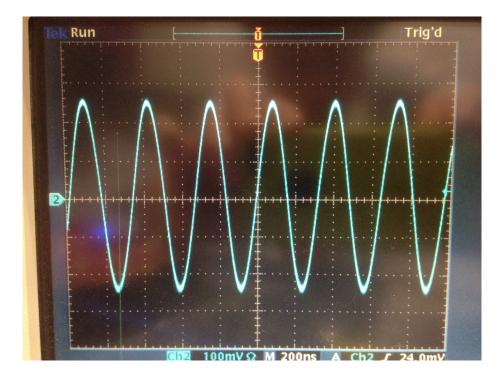

To perform short transport layer test, you must properly set up the pattern checker at DAC transport layer according to the following steps:

- 1. Set bit 12 of the config2 register (address 0x02) to enable short transport layer checker. To do this, highlight the config2 register and check the bit 12 checkbox in the "DAC3XJ8X Controls > Low Level View" tab. Click the **Write Register** button to write the setting to the SPI interface of the DAC37J84.

- 2. Clear bits 8–15 of the config6 register (address 0x06) to disable the "Short Test Error" alarm mask. Clear the bits according to the respective active lanes (for example, bit 8 is for lane0, bit 15 is for lane 7).

To do this, uncheck the **Short Test Error** checkboxes at the *Alarm Masking* section in the "DAC3XJ8X Controls > Alarms and Errors" tab.

- **3.** Set the FPGA to output the corresponding test pattern, according to the parameter configuration listed in **Table 6**.

- **4.** Check the result at bits 8–15 of the config109 register. To do this, press the **Clear Alarms and Read** button in the "DAC3XJ8X Controls > Alarms and Errors" tab and monitor the **Short Test Error** indicator.

#### Figure 9: DAC3XJ8X Controls Tab - Alarms and Errors

| File       Debug       Settings       Help         DAC3XJ8X CONtrols       LMK04828 Controls       Low Level View       Circick ALARMS       USB Status       Reconnect USB ?         Quick Start       DAC3XJ8X Controls       LMK04828 Controls       Low Level View       Circick ALARMS       USB Status       Reconnect USB ?         Overview       Clocking       SERDES and Lane Configuration       JESD Block       Dig Block 1       Dig Block 2       Alarms and Errors         The DAC3XJ8X atams are "stick/". Meaning that if an atam occurs, it will constantly report that atam unit is closered, the adarms buto no bease to check if an atam oper-operation conserved, the "Read Atarms" buton conserved, th                                                                                                                                                                                     | A DAC3XJ8X GUI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                  |                       |                        |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------|------------------------|--|--|--|--|

| Quick Start       DAC3XJ8X Controls       LMK04828 Controls       Low Level View       Chick ALARMS       USB Status       Reconnect USB ?         Overview       Clocking       SERDES and Lane Configuration       JESD Block       Dig Block 1       Dig Block 2       Alarms and Errors         The DAC3XJ8X airms are "sticky". Meaning that if an airm occurs, it will constantly report that and proper operation observed, the "Read Alarms" button to check the alarms. After the alarms. Afte         | File Debug Settings Help                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                  |                       |                        |  |  |  |  |

| Clocking       SERDES and Lane Configuration       JECK LOGO FORM       Click Color       Alarms and Errors         Alarms and Read butin to check the alarms. After the alarms have been cleared and proper operation observed, the "Read Alarms" butino can be used to check if an alarm has occure. After the alarms have been cleared and proper operation observed, the "Read Alarms" butino can be used to check if an alarm has occure. After the alarms have been cleared and proper operation observed, the "Read Alarms" butino can be used to fock if an alarm has occure. The alarms for the Color of "FFO Read Error FFO Read Error                                                                                                                | DAC3XJ8X GUI v1.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                  |                       |                        |  |  |  |  |

| Otor work       Outcoming                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Quick Start         DAC3XJ8X Controls         LMK04828 Controls         Low Level View         Check ALARMS         USB Status         Reconnect USB ?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                  |                       |                        |  |  |  |  |

| The DAC3XJBX alarms are "sticky". Meaning that if an alarm occurs, it will constantly report that<br>alarm until it is cleared. The alarms only have meaning when the DAC is configured and running<br>property. Cick the "Clear Alarms and Read" button to check the alarms have been<br>has occured. Only alarms on enabled RX lanes are valid if "FFO Read Error" or "FFO Read Error" or "FFO Read Error" or "FFO Read Error" or<br>is observed, reset the JESD core and trigger SYSREF again.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Overview Clocking SERDES and Lane Configur                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ation JESD Block | Dig Block 1 Dig Block | 2 Alarms and Errors    |  |  |  |  |

| Alarm Zeros JESD Data       DAC PLL Out of Lock       Frame Alignment Error         Alarm Mid-Levels DAC       ALARM Pin         Alarm Output       Image: Construction of Lock       SERDES PLL 0 Out of Lock         Alarm Alignment Error       Link Configuration Error         Alarm Pin       Image: Construction of Lock         Alarm Output       Image: Construction of Lock         ALARM Pin       Code Group Synch. Error         ALARM Pin Polarity       Code Group Synch. Error         Active High       Image: Code Group Synch. Error         Ater Masking       Difference         SYSREF Errors       Image: Code Group Synch. Error         Short Test Error       Image: Code Group Synch. Error         Short Test Error       Image: Code Group Synch. Error         Short Test Error       Image: Code Group Synch. Error         Error Counting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | The DAC3XJ8X alarms are "sticky". Meaning that if an alarm occurs, it will constantly report that alarm until it is cleared. The alarms only have meaning when the DAC is configured and running properly. Click the "Clear Alarms and Read" button to check the alarms. After the alarms have been cleared and proper operation observed, the "Read Alarms" button can be used to check if an alarm has occured. Only alarms on enabled RX lanes are valid. If "FIFO Read Error" or "F |                  |                       |                        |  |  |  |  |

| Alarm Mid-Levels DAC         ALARM Pin         Alarm Output         Alarm Output         ALARM Pin         Alarm Nid-Levels DAC         ALARM Pin         Alarm Number         ALARM Pin Polarity         Active High         ATEST b 000000         0       1         0       1         2       Code Group Synch. Error         PA Protection Alarms       8b/10b Not-in-Table Error         0       1       2         0       1       2         0       1       2         ATEST b 000000       0       1         0       1       2         0       1       2         0       1       2         0       1       2         0       1       2         0       1       2         0       1       2         0       1       2         0       1       2         0       1       2         0       1       2         0       1       2         0       1       2         0 <th>DAC PLL Out of Look</th> <th></th> <th></th> <th></th>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | DAC PLL Out of Look                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                  |                       |                        |  |  |  |  |