شرح دوره های آموزشی ویدئویی

این آموزشها بصورت ویدئوهای فارسی هستند و فقط برای مشتریان داخل ایران آرتمیس کاریا در دسترس می باشند

دوره های آموزشی ویدئویی

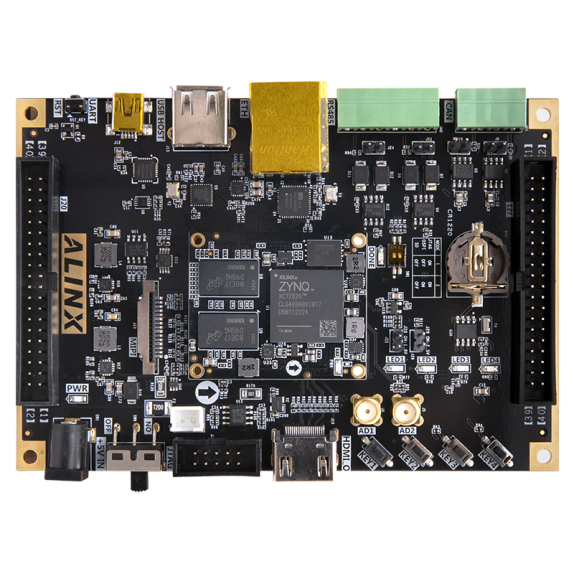

آموزش مفاهیم و کاربری تراشه های زینک (1)

با شرکت در این دوره آموزشی ضمن آشنایی کامل با تراشه زینک ، با کاربری و نحوه کد دهی و برنامه ریزی این تراشه تا سطح متوسط آشنا خواهید شد.

آموزش کاربری پیشرفته تراشه های زینک (2)

در این دوره آموزشی نحوه کاربری تراشه های زینک از سطح متوسط تا پیشرفته را خواهید آموخت.

دوره کار با HLS

آموزش استفاده از ابزار HLS که شتابدهنده و تسریع کننده پیاده سازی طراحی های ایجاد شده برای اف پی جی ای ها می باشد.

دوره آموزش کار با Linux

فراگیری نحوه بکارگیری بخش آرم در تراشه زینک.

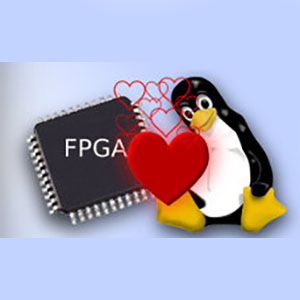

آموزش اجرای پایتون بر روی بردهای زینک

این آموزش بزودی برگزار خواهد شد

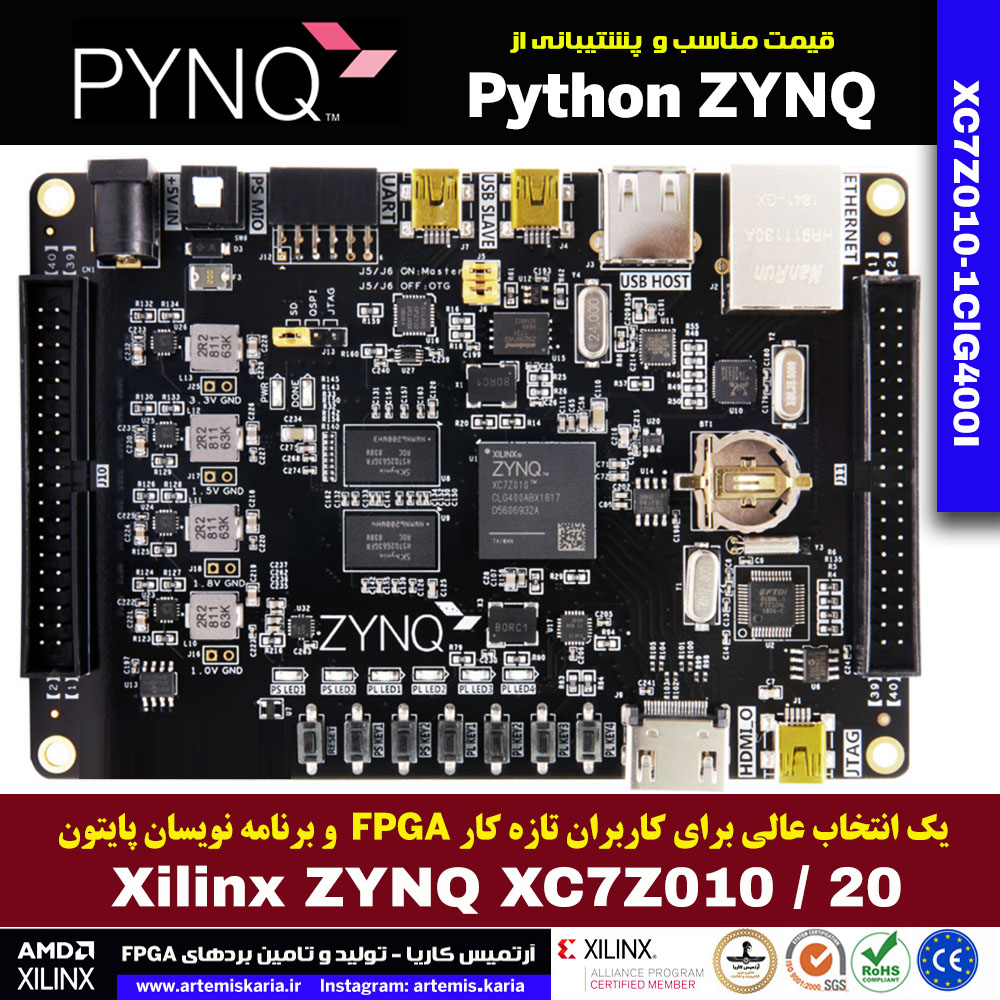

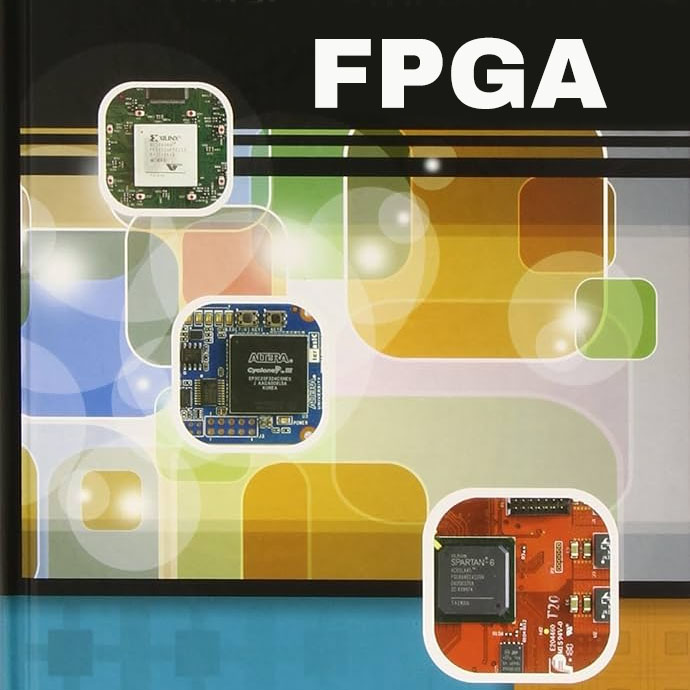

FPGA

این آموزش در حال تولید است. آموزش موثر و کاربردی طراحی و کار با تراشه های FPGA در سطح مقدماتی

VHDL

این آموزش در حال تولید است. این درس پایه ورود به دنیای مهندسی FPGA می باشد و تبحر در آن لازم و کارساز است

شرح دوره های آموزش ویدئویی برای تراشه های زینک

از سطح مقدماتی تا پیشرفته

آشنایی با SoC و معرفی ZYNQ

معرفی محیط VIVADO

معرفی محیط SDK

پروگرام و دیباگ

کار با Peripheral ها و ابزار های جانبی

کتابخانه های Middleware برای شبکه و FAT

تنظیمات PS، معرفی TCL و Definition Board

AXI BUS

معرفی ILA و چیپ اسکوپ

نوشتن کد HDL و ساخت IP Core دلخواه

ارتباط PS و PL

معرفی HLS و برنامه نویسی ++C برای FPGA

معرفی لینوکس روی ZYNQ

سرفصل های دوره آموزشی زینک مقدماتی (زینک 1):

معرفی دوره آموزشی مفهومی و کاربردی ZYNQ مجموعه آرتمیس کاریا

زمان آن فرا رسید تا دانش انباشته شده در زمینه طراحی سامانه های مبتنی بر تراشه های FPGA را به تمام علاقمندان دنیای الکترونیک و فناوری منتقل کنیم .

📣این دوره آموزشی که بخشی از سلسله آموزش های طراحی شده توسط مجموعه آرتمیس کاریا میباشد ، بصورت دوره های آموزش ویدئویی ارائه میگردند . اصول و ساختار تراشه های خانواده ZYNQ7000 ، نحوه کار با نرم افزار ها و ابزار های کاربردی مرتبط ، پریفرال ها و کتابخانه ها و همچنین تکنیک های کار با این تراشه ها به گونه ای آموزش داده میشود تا دانشجو در پایان این دوره بتواند مفاهیم یک سامانه FPGA محور را درک و طراحی کند .